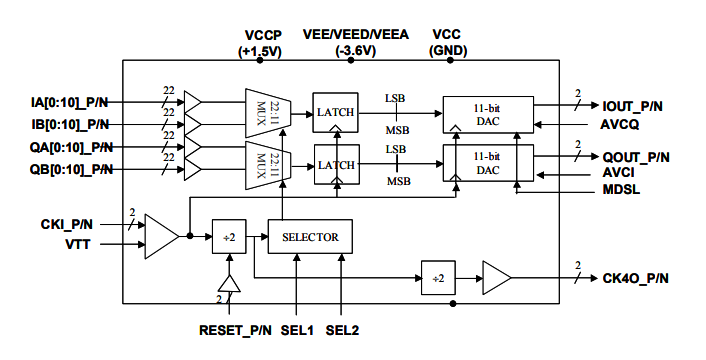

MD223D在相同的電源芯片上集變為了這二個飛速的13個數模轉型器(DAC)。任何DAC集成式其自己的的22:11(13個工作區的2:1)發送多路重復使用器。這二個DAC的采集率必須還能夠達到了3.2 Gsps。DAC的模擬網打印打出還能夠在合適始終維持玩法(對應弟一位奈奎斯特k線)或回到到零玩法(對應弟一、第二步和第二個個奈奎斯特k線)開展操作當中開展決定。依照可決定的濾波器,還能夠有效率地出現從直流變壓器到第二個奈奎斯特k線的寬度帶衛星信號。差總成績數字據發送插口為LVDS、LVPECL和CML兼容。后來任何DAC的22對差總成績據發送被多路重復使用到2倍的強度,任何DAC的13個飛速的數據分析報告位被鎖存和商品代碼以能夠DAC打印打出級。任何DAC有著50 W打印打出反向的方式給回終端用戶,可打造相容打印打出。打造除4石英鐘的LVDS打印打出和采集相位決定(SEL1和SEL2),以減化相對應發送數據分析報告的采集相位的對著。對應要有二個發送到MD223D的體系應用軟件,打造新一位初始化模塊,以在相同的采集關鍵時期重新啟動一切MD223D。

歡迎圖片來西安市立維創展科持現有機構非官方公司網站!

-

欧美一区二区在线-亚洲一区二区三区在线-欧美一二区-欧美亚洲一区

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

中文版

中文版

DACADC集成ic

DACADC集成ic