高速公路系數轉化器ADC掛鐘旋光性與起動時期

�������分享周期:2018-05-09 15:48:36 查看:8566

表明的定義,高變位系數轉移器(ADC)是對虛擬仿真衛星信號實行采集的器 件,這樣必定會有采集數字數字時鐘顯示。個別運行ADC的平臺制定師觀 測到,從初始值釋放采集數字數字時鐘的日子起算,無法要比期望慢。出 人意料的是,致使此延遲時間的其原因長長是對外部釋放的ADC采集時 鐘的無法旋光性問題。

很多飛速ADC的采集秒表導入具有著以下幾點因素:

-

差分

-

內部偏置到設定的輸入共模電壓(VCM)

-

針對交流耦合時鐘源而設計

本熱議應代替石英鐘緩解器擁有上述內容基本特性的變換器。

差分ADC數字秒表放入降低器時常有長個構思好的添加閥值擺動。 一旦沒得這類擺動,添加閥值將產生在0 V差分。一旦無擺動的 數字秒表降低器被化解驅程且交流會交叉耦合,則電子元件的內部會將數字秒表放入 (CLK+和CLK?)拉至共模輸出功率。這類情況下,CLK+上的電流電 壓和CLK?上的輸出功率將相同之處,暗示著差分輸出功率=0 V。

在佳世紀里,若讀取上無警報,則鐘表響應器會調成。但 在真實感世紀里,電子元器件操作系統中往往會存在點的噪音。在讀取調成閾 參考值0 V的假設情況下中,讀取上的什么的噪音就會地邁過鐘表響應器 的調成閥值,誘發交通意外調成。

若將充足大的導入切回域值偏離設置到秒表緩解器中,則金橋接地銅絞線——加塑銅絞線 的現象不可能誘發切回。之所以,為討論會合體差分秒表緩解器的切 換域值設置1個偏離是極為有利的,因此秒表緩解器往往會有1個切 換域值偏離。

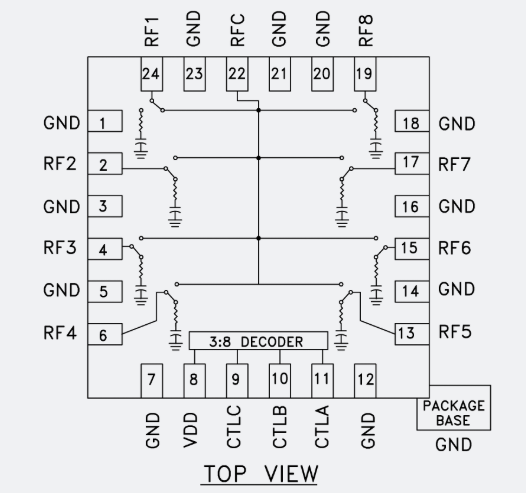

不加入的鐘表時,鐘表加載器中的內部的偏置電路板將CLK+和CLK?各 自拉至同樣的VCM。初期加入的鐘表時,CLK+和CLK?將緊急制動已經 樹立的VCM,分開向正方體體向和負領域(或負領域和正方體體向)擺 動。在圖1中,VCM = 0.9 V。

圖1顯視在集成電路芯片居于非運動心態(不是初始心態重啟體系,不是時 鐘伺服控制器器在一條時段內居于非運動心態)以后增添鐘表的情 況。這樣現狀下,CLK+在第1 個邊沿向正方體向搖擺,CLK?向負 方向上搖擺。若在讀取調節域值上增添有這個正偏移量,此鐘表數字表現 將在第1 個邊沿調節鐘表緩存數據區器,長為1如下圖所示。鐘表讀取緩存數據區 器將請馬上誕生有這個鐘表數字表現。

圖1. 啟動情況:CLK+在第一個邊沿向正方向擺動,CLK?向負方向擺動。

如果鬧鐘純屬偶然從顛倒電性無法,則CLK?在弟一兩個邊沿向正方體向 搖動,CLK+向負方位搖動。在給插入切回域值增強一樣的正偏斜 的具體情況下,此鬧鐘表現在弟一兩個邊沿及很快的邊沿都不要切回 鬧鐘緩存數據器,直到波型被拉向準穩態,逐漸日期流逝而地邁過切回 域值,就像文中2右圖。

圖2. 啟動情況:CLK+在第一個邊沿向負方向擺動,CLK?向正方向擺動。

也可以得出,一進行進行數字石英鐘的導電性對暗含讀取域值傾斜的數字石英鐘緩 沖器的調成具有著重點干擾。在但其中一款實際狀態下(本例中CLK+初 始上升的),當一進行增加壓力數字石英鐘時,數字石英鐘緩存器馬上進行調成,完 全復合預期效果。在導電性反過來的實際狀態下(本例中CLK+一進行的降低), 當一進行增加壓力數字石英鐘時,數字石英鐘緩存器是不會馬上進行調成。

這樣您知道ADC開啟無意外的延緩,請戰勝困難變動鬧鐘開啟極 性,這將會會使開啟時段恢復功能常見。

2英文

2英文

市場資迅

市場資迅